#### **Features**

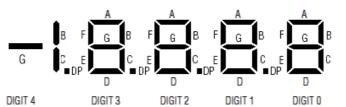

- Max. ±19,999 counts

- QFP-44L package

- Input full scale range: 200mV or 2V

- Built-in multiplexed **LED** display driver: 4-1/2 digits, 4 decimal points and polarity

- Underrange/Overrange outputs

- 10µV resolution on 200mV scale

- Display Hold

- Precise 10:1 range select

- True differential input and reference

- Built-in inverters for RC oscillation circuit.

#### **Application**

Panel Meter

#### **Description**

ES5128 is a 19,999-count analog-to-digital converter (ADC) with multiplexed LED display driver. It drives 4-1/2 digits, 4 decimal points and polarity segments. It typically requires a dual +5V/-5V power supply or a 10V single power with 5V regulator, like 7905 series ICs, for ADC operation. ES5128 has a ±19,999 counts resolution on both 200.00mV 2.0000VIt features high and ranges. inputs, excellent differential impedance linearity, true ratiometric operation and auto polarity. The underrange and overrange outputs and the 10:1 range changing inputs facilitate the design of autoranging systems. Other features include Display Hold and controllable decimal points.

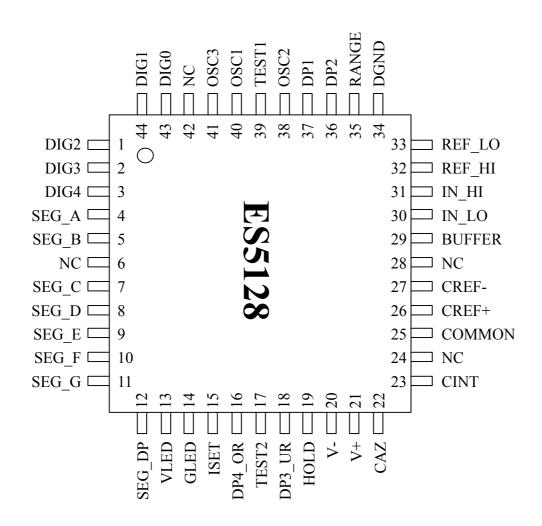

## **Pin Assignment**

QFP-44L

## **Pin Description**

## QFP-44L

| Pin No | Symbol | Type | Description                                                           |  |  |

|--------|--------|------|-----------------------------------------------------------------------|--|--|

| 1      | DIG2   |      | LED backplane signal for DIG2                                         |  |  |

| 2      | DIG3   | О    | LED backplane signal for DIG3                                         |  |  |

| 3      | DIG4   | О    | LED backplane signal for most significant digit                       |  |  |

| 4      | SEG A  | О    | LED segment signal for all A segments                                 |  |  |

| 5      | SEG B  | O    | LED segment signal for all B segments                                 |  |  |

| 6      | NC     |      |                                                                       |  |  |

| 7      | SEG C  | О    | LED segment signal for all C segments                                 |  |  |

| 8      | SEG D  | О    | LED segment signal for all D segments                                 |  |  |

| 9      | SEG E  | О    | LED segment signal for all E segments                                 |  |  |

| 10     | SEG F  | О    | LED segment signal for all F segments                                 |  |  |

| 11     | SEG G  | О    | LED segment signal for all G segments                                 |  |  |

| 12     | SEG DP | О    | LED segment signal for all decimal point segments                     |  |  |

| 13     | VLED   | P    | Positive power supply for LED driver circuit                          |  |  |

| 14     | GLED   | P    | Negative power supply for LED driver circuit                          |  |  |

| 15     | ISET   | О    | Adjust the bright(current) of LED segment.                            |  |  |

| 16     | DP4_OR | I/O  | Input: Turns on most significant decimal point when HI.               |  |  |

|        | _      |      | Output: Pulled HI when result count exceeds ±19,999.                  |  |  |

| 17     | TEST2  | _    | TEST pin. Not Connect.                                                |  |  |

| 18     | DP3_UR | I/O  | Input: Turn on the 2 <sup>nd</sup> significant decimal point when HI. |  |  |

|        |        |      | Output: Pulled HI when result count is less than $\pm 1,000$ .        |  |  |

| 19     | HOLD   | I/O  | Input: when floating, ES5128 operates in the free-run                 |  |  |

|        |        |      | mode. When pulled high, the last display reading is held.             |  |  |

|        |        |      | When pulled LO, the result counter contents are shown                 |  |  |

|        |        |      | incrementing during the de-integrate phase of cycle.                  |  |  |

|        |        |      | Output: Negative going edge occurs when the data latches              |  |  |

|        |        |      | are upgraded. Can be used as a converter status signal.               |  |  |

| 20     | V-     | P    | Negative power supply terminal                                        |  |  |

| 21     | V+     | P    | Positive power supply terminal                                        |  |  |

| 22     | CAZ    | I/O  | Integrator amplifier input                                            |  |  |

| 23     | CINT   | I/O  | Integrator amplifier output                                           |  |  |

| 24     | NC     |      |                                                                       |  |  |

| 25     | COMMON | О    | Set common-mode voltage of 3.2V below V+.                             |  |  |

| 26     | CREF+  | О    | Positive connection to external reference capacitor                   |  |  |

| 27     | CREF-  | О    | Negative connection to external reference capacitor                   |  |  |

| 28     | NC     |      |                                                                       |  |  |

| 29     | BUFFER | О    | Buffer amplifier output                                               |  |  |

| 30     | IN_LO  | I    | Negative input voltage terminal                                       |  |  |

| 31     | IN_HI  | I    | Positive input voltage terminal                                       |  |  |

| 32     | REF_HI | I    | Positive reference voltage terminal                                   |  |  |

| 33     | REF_LO | I    | Negative reference voltage terminal                                   |  |  |

| 34     | DGND   | О    | Ground reference for digital section                                  |  |  |

| 35 | RANGE | I   | Pulled HIGH externally for 2V scale.                  |  |

|----|-------|-----|-------------------------------------------------------|--|

| 36 | DP2   | I   | When HI, decimal point 2 will be on.                  |  |

| 37 | DP1   | I   | When HI, decimal point 1 will be on.                  |  |

| 38 | OSC2  | I/O | Output of first clock inverter. Input of second clock |  |

|    |       |     | inverter.                                             |  |

| 39 | TEST1 | -   | TEST pin. Not connect.                                |  |

| 40 | OSC1  | I/O | Input of first clock inverter.                        |  |

| 41 | OSC3  | О   | Output of second clock inverter.                      |  |

| 42 | NC    |     |                                                       |  |

| 43 | DIG0  | О   | LED backplane signal for DIG0                         |  |

| 44 | DIG1  | О   | LED backplane signal for DIG1                         |  |

## **Absolute Maximum Ratings**

| Characteristic                  | Rating                 |

|---------------------------------|------------------------|

| Supply Voltage (V+ to V-)       | 15V                    |

| Analog Input Voltage            | V0.6 to V+ +0.6        |

| Digital Input                   | DGND -0.6V to V+ +0.6V |

| Power Dissipation. Flat Package | 500mW                  |

| Operating Temperature           | 0°C to 70°C            |

| Storage Temperature             | -25°C to 125°C         |

### **Electrical Characteristics**

TA=25°C, 10V between V+ and V-

| Parameter                                    | Test Condition          | Min. | Тур. | Max   | Units  |

|----------------------------------------------|-------------------------|------|------|-------|--------|

| Zero input reading                           | Vin=0, 200mV scale      | -1   | 0    | 1     | counts |

| Ratiometric reading                          | Vin=Vref=1V<br>Range=2V | 9998 | 9999 | 10000 | counts |

| Rollover Error                               | +Vin=-Vin=199mV         | _    | _    | 2     | counts |

| Linearity Error                              | 200mV Scale             |      |      | 1     | counts |

| Common Voltage                               | V+ to Common            | 2.8  | 3.2  | 3.5   | V      |

| Common Sink Current                          | $\Delta$ common=+0.1V   | 0.1  | 2    |       | mA     |

| Common Source Current                        | ∆ common=-0.1V          | 10   | 200  |       | μΑ     |

| Supply Current excluding LED display current | V+ to V- = 10V          |      | 0.9  | 1.4   | mA     |

| Supply Voltage Range                         | V+ to V-                | 7    | 10   | 14    | V      |

## **Function Description**

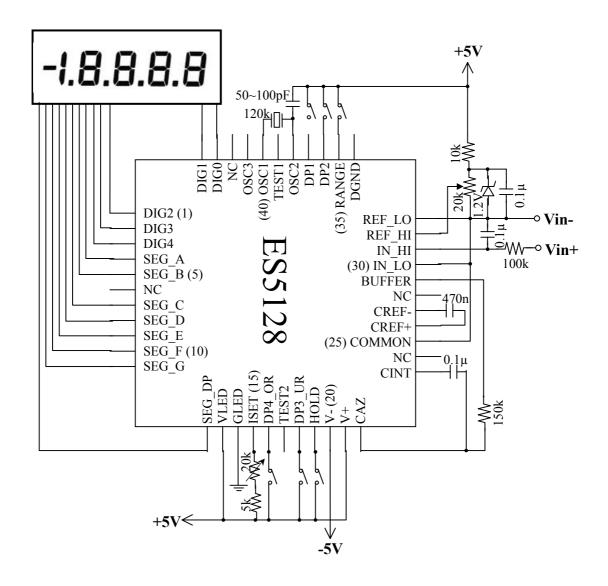

#### 1. Normal Operation

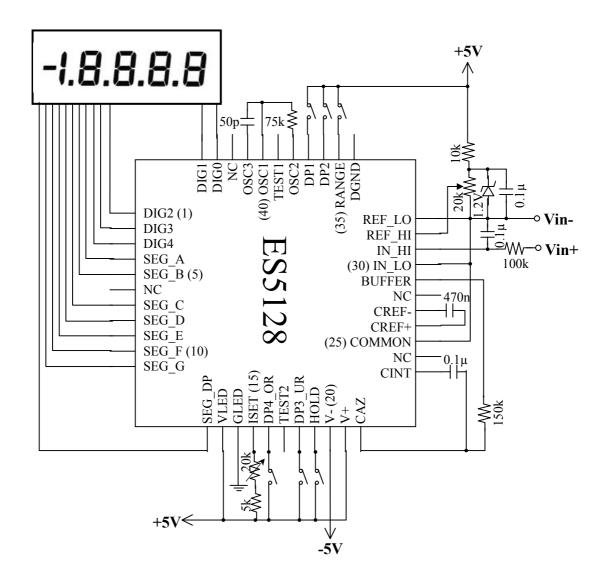

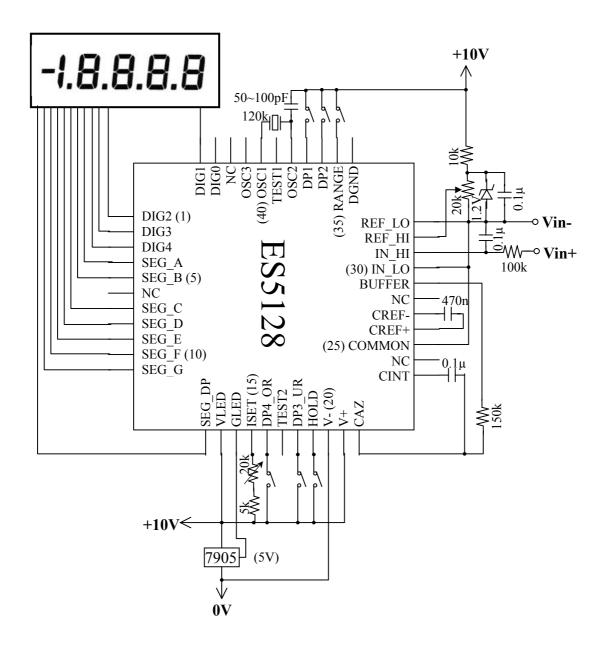

When ES5128 operates at the oscillation frequency of 120KHz, the conversion period will be 500ms. And the less frequency it has, the longer time it takes to complete one conversion. ES5128 takes input signal from pins IN\_LO and IN\_HI differentially, and take reference from pins REF\_LO and REF\_HI. The typical reference voltage is about 1V. A filter capacitor and a protective resistor are recommended at IN\_HI and IN\_LO terminal as the test circuit of page7.

#### 2. Range Change Function

ES5128 has 2 operation ranges such as 200.00mV and 2.0000V. When the pin RANGE is pulled to DGND or keep floating, ES5128 operates at 200.00mV full-scale range. When it is pulled to V+, ES5128 change the input full-scale range to 2.0000V. And the output data still remain the maximum counting number  $\pm 19,999$ .

#### 3. Data Hold Function

ES5128 support a data hold function to stop the LED panel upgrading and hold the final data. When the pin HOLD keeps floating, ES5128 operates in free run mode, and the data upgrades after every conversion. When it is pulled to V+, ES5128 enters HOLD mode, the LED panel stops upgrading the output data, And the final data before the HOLD mode is activated is held.

#### 4. Decimal Points Controlled

ES5128 can drive 4 decimal points on LED panel. It provides four pins DP1, DP2, DP3 and DP4 to control the decimal points. Connect the pins DP1~DP4 to V+ will turn on the relative decimal points. To turn it off, keep it floating or connect it to DGND.

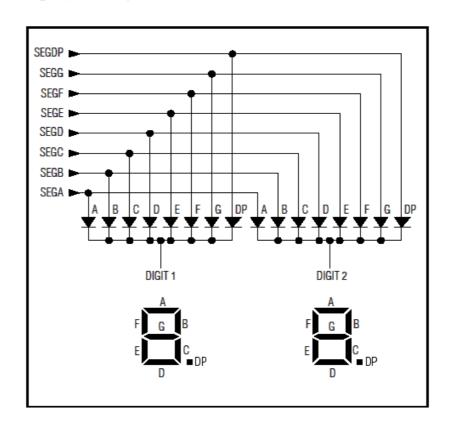

### 5. LED Display Configuration

|      | SEG_A | SEG_B | SEG_C | SEG_D | SEG_E | SEG_F | SEG_G | SEG_DP |

|------|-------|-------|-------|-------|-------|-------|-------|--------|

| DIG0 | 0A    | 0B    | 0C    | 0D    | 0E    | 0F    | 0G    |        |

| DIG1 | 1A    | 1B    | 1C    | 1D    | 1E    | 1F    | 1G    | DP1    |

| DIG2 | 2A    | 2B    | 2C    | 2D    | 2E    | 2F    | 2G    | DP2    |

| DIG3 | 3A    | 3B    | 3C    | 3D    | 3E    | 3F    | 3G    | DP3    |

| DIG4 |       | 4B    | 4C    |       |       |       | SIGN  | DP4    |

## **Test Circuit – 120KHz Crystal Oscillator**

#### **Test Circuit – RC Oscillation Circuit**

## **Test Circuit – Single Power operation**

## ES5128

## 4-1/2 digit with LED

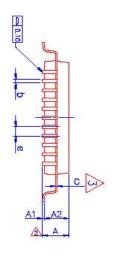

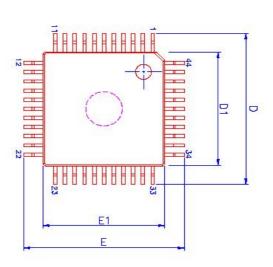

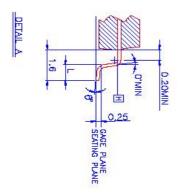

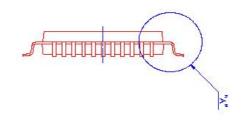

## **Product Outline: QFP-44**

|   | SYMBOLS | MIN.        | NOM       | MAX.  |  |  |

|---|---------|-------------|-----------|-------|--|--|

|   | A       | _           |           | 2.7   |  |  |

| ^ | A1      | 0.25        | 0.30      | 0.35  |  |  |

| 3 | A2      | 1.9         | 2.0       | 2.2   |  |  |

|   | b       | 0.3 (TYP.)  |           |       |  |  |

|   | D       | 13.00       | 13.20     | 13.40 |  |  |

|   | D1      | 9.9         | 10.00     | 10.10 |  |  |

|   | E       | 13.00       | 13.20     | 13.40 |  |  |

|   | E1      | 9.9         | 10.00     | 10.10 |  |  |

|   |         | 0.73        | 0.88      | 0.93  |  |  |

|   | е       | 0.80 (TYP.) |           |       |  |  |

| ^ | O°      | 0           | For-A 119 | 7     |  |  |

| 3 | C       | 0.1         | 0.15      | 0.2   |  |  |

UNIT: mm

#### NOTES:

1.JEDEC OUTLINE:MO-108 AA-1

2.DATUM PLANE HIS LOCATED AT THE BOTTOM OF THE MOLD PARTING LINE COINCIDENT WITH WHERE THE LEAD EXITS THE BODY.

3.DIMENSIONS D1 AND E1 DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 mm PER SIDE. DIMENSIONS D1 AND E1 DO INCLUDE MOLD MISMATCH AND ARE DETERMINED AT DATUM PLANE [H].

4.DIMENSION 6 DOES NOT INCLUDE DAMBAR PROTRUSION.