## Features

- Max. 11,000 counts resolution

- Conversion rate selectable by MPU command: 1.6/s → 128/s

- Input signal full scale: 110mV

- 50/60Hz line noise rejection selectable by MPU command

- Low battery detection

- Multiple input channels for ADC

- 3-wire serial bus and EOC signal for MPU I/O port

- -3V power operation with internal charge pumping circuit

- MPU I/O power level selectable by external control pin

- Zero calibration for eliminating offset error

- On-chip buzzer driving and frequency selectable by MPU command

- Support sleep mode by external CS(chip-select) pin

# Application

Clamp meter Thermometer Portable instrumentation

# Description

ES51992 is an 11000-count dual-slope analogto-digital converter (ADC). The conversion rate and buzzer frequency can be selected or decided by an external microprocessor. The conversion rate can be varied from 1.6 time/sec to 128 times/sec under 4MHz/12MHz crystal oscillation clock. Besides, ES51992 also provides multi-channels input, low battery detection, power-down mode, 50/60Hz line noise rejection selection, and I/O port level selection for flexible design.

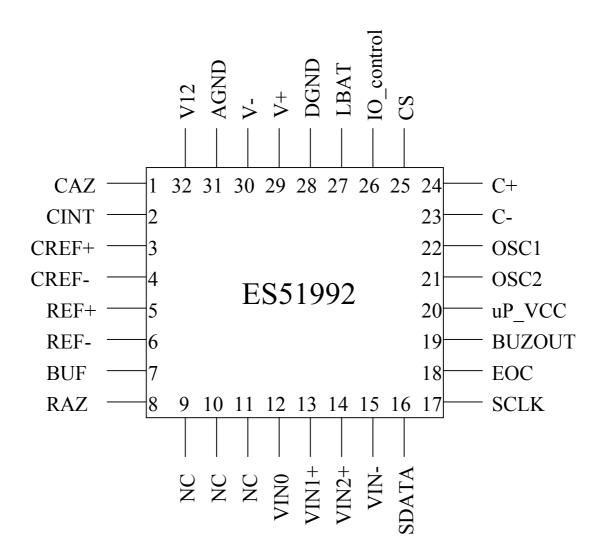

# **Pin Assignment**

# LQFP-32L

承永資訊科技 CYRUSTEK CO.

# **Pin Description**

| Pin No | Symbol      | Туре | Description                                                            |  |

|--------|-------------|------|------------------------------------------------------------------------|--|

| 1      | CAZ         | Ι    | Auto-zero capacitor connection.                                        |  |

| 2      | CINT        | 0    | Integrator output. Connect to integral capacitor                       |  |

| 3      | CREF+       | I/O  | Positive connection for reference capacitor.                           |  |

| 4      | CREF-       | I/O  | Negative connection for reference capacitor.                           |  |

| 5      | REF+        | Ι    | Differential reference high voltage input.                             |  |

| 6      | REF-        | Ι    | Differential reference low voltage input.                              |  |

| 7      | BUF         | 0    | Buffer output pin. Connect to integral resistor                        |  |

| 8      | RAZ         | 0    | Buffer output pin in high-speed mode. Connect to high-speed integral   |  |

|        |             |      | resistor.                                                              |  |

| 9      | NC          | -    | Not connected                                                          |  |

| 10     | NC          | -    | Not connected                                                          |  |

| 11     | NC          | -    | Not connected                                                          |  |

| 12     | VIN+        | Ι    | Analog differential high signal input.                                 |  |

| 13     | VIN1+       | Ι    | Analog signal high input1                                              |  |

| 14     | VIN2+       | Ι    | Analog signal high input2                                              |  |

| 15     | VIN-        | Ι    | Analog differential low signal input.                                  |  |

| 16     | SDATA       | I/O  | Serial data I/O pin. Nch open-drain output.                            |  |

| 17     | SCLK        | Ι    | Serial clock input pin.                                                |  |

| 18     | EOC         | 0    | An indicator for ADC conversion ending.                                |  |

| 19     | BUZout      | 0    | Buzzer frequency output                                                |  |

| 20     | uP_VCC      | Ι    | MPU I/O port power level selection                                     |  |

| 21     | OSC2        | 0    | Crystal oscillation connection                                         |  |

| 22     | OSC1        | Ι    | Crystal oscillation connection                                         |  |

| 23     | С-          | 0    | Negative capacitor connection for on-chip DC-DC converter.             |  |

| 24     | C+          | 0    | Positive capacitor connection for on-chip DC-DC converter.             |  |

| 25     | CS          | Ι    | Chip select input pin. Pull to Low to enter power down mode.           |  |

| 26     | I/O_control | Ι    | MPU I/O port ground level selection                                    |  |

| 27     | LBAT        | Ι    | Low battery configuration. If 3V battery is used, connect it to AGND.  |  |

|        |             |      | The default low-battery threshold voltage is -2.3V. If 9V or other     |  |

|        |             |      | battery voltage is used, the low battery annunciator is displayed when |  |

|        |             |      | the voltage of this pin is less than V12                               |  |

| 28     | DGND        | G    | Digital ground                                                         |  |

| 29     | V+          | O/P  | Output of on-chip DC-DC converter.                                     |  |

| 30     | V-          | Р    | Negative supply voltage. Connecting to 3V battery negative terminal.   |  |

| 31     | AGND        | G    | Analog ground                                                          |  |

| 32     | V12         | 0    | Output of band-gap voltage reference. Typically -1.23V                 |  |

# **Function description**

### 1. Dual Slope A/D-Four Phases Timing

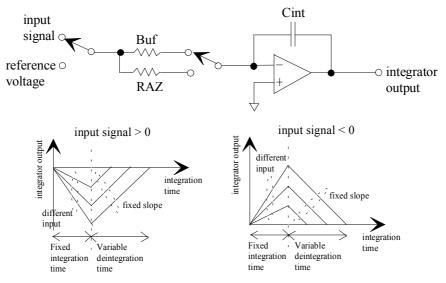

ES51992 is a dual-slope analog-to-digital converter (ADC). Figure 1 is a structure of dual-slope integrator. Its measurement cycle has two distinct phases: input signal integration (INT) phase and reference voltage integration (DINT) phase.

In INT phase, the input signal is integrated for a fixed time period, then A/D enters DINT phase in which an opposite polarity constant reference voltage is integrated until the integrator output voltage becomes to zero. Since both the time period for input signal integration and the amount of reference voltage are fixed, thus the de-integration time is proportional to the input signal. Hence, we can define the mathematical equation about input signal, reference voltage integration (see Figure 1.):

$$\frac{1}{Buf \times C \operatorname{int}} \int_{0}^{T_{INT}} V_{IN}(t) dt = \frac{1}{Buf \times C \operatorname{int}} \times V_{REF} \times T_{DINT}$$

where,  $V_{IN}(t) = \text{input signal}$

$V_{REF}$  = reference voltage  $T_{INT}$  = integration time (fixed)  $T_{DINT}$  = de-integration time (proportional to  $V_{IN}(t)$ )

Figure 1. the structure of dual-slope integrator and its output waveform.

If  $V_{IN}(t)$  is a constant, we can rewrite above equation:

$$T_{DINT} = \frac{T_{INT}}{V_{REF}} \times V_{IN}$$

# **ES51992** 11,000 Counts ADC

Besides the INT phase and DINT phase, ES51992 exploits auto zero (AZ) phase and zero integration (ZI) phase to achieve accurate measurement. In AZ phase, the system offset is stored. The offset error will be eliminated in DINT phase. Thus a higher accuracy could be obtained. In ZI phase, the internal status will be recovered quickly to that of zero input. Thus the succeeding measurements won't be disturbed by current measurement especially in case of overload.

As mentioned above, the measurement cycle of ES51992 contains four phases:

- (1) auto zero phase (AZ)

- (2) input signal integration phase (INT)

- (3) reference voltage integration phase (DINT)

- (4) zero integration phase (ZI)

The time ratios of these four phases, AZ, INT, DINT and ZI to the entire measurement cycle are 8.8%, 32%, 35.2% and 24% respectively. However the actual duration of each phase depends on conversion rate. An example is shown in the table below. A user can easily deduce other cases based on the table.

Voltage:

| CR (times/sec) | ZI (ms) | AZ (ms) | INT (ms) | DINT (ms) |

|----------------|---------|---------|----------|-----------|

| 8              | 30      | 11      | 40       | 44        |

Note: reference voltage = -100 mV.

Voltge+PEAK:

| CR (times/sec) | ZI (ms) | AZ (ms) | INT (ms) | DINT (ms) |

|----------------|---------|---------|----------|-----------|

| 8              | 30      | 11      | 40       | 60        |

Note: reference voltage = -100 mV.

## 2. Component Value Selection for ADC

For various application requirements on conversion rate and input full range, we suggest nominal values for external components of ADC in Figure 1 to obtain better performance. Under default condition with operating clock = 12 MHz:

(1) conversion rate = 8 times/sec

(2) reference voltage = -100 mV

(3) input signal full scale = 110 mV (sensitivity = 10 uV)

We suggest that Cint = 68 nF, Buf = 56 k $\Omega$

If a user selects a different conversion rate rather than default, the integration capacitor Cint value must be changed according to the following rule for better performance:

Cint  $\times$  (conversion rate) = (68 nF)  $\times$  (8 times/sec).

A smaller Cint reduces the input full range. However a larger Cint might have weaker noise immunity than the suggested one.

A user could enlarge the input full range by changing reference voltage (Vref) and the amount of integration resistor (Buf). For example, if Vref & Buf are enlarged as twice than the default values then the input full range becomes 220 mV. The input full range can be enlarged up to 1.1V (10 times than the default case). We list general rules in below which might be helpful in determining component values.

Buf / (reference voltage) = 56 k $\Omega$  / (-100 mV)

# 3. Multi Channel Input

ES51992 provides VIN+, VIN1+, VIN2+ and Vin- pins to achieve the multi channel input (multiplexer) feature. Because ES51992 is a single core A-to-D converter, it can only process one pack of data per conversion period. Although it has four input pins, it would take only one pair as input channel from the four pins. The actual input channel is determined by the bits CH1/CH0 of STATUS Byte1 as the following table:

| Input Channel | CH1 | CH0 | High Input | Low Input |

|---------------|-----|-----|------------|-----------|

| ch1           | 0   | 0   | VIN+       | VIN-      |

| ch2           | 0   | 1   | VIN1+      | VIN-      |

| ch3           | 1   | 0   | VIN2+      | VIN-      |

| ch4           | 1   | 1   | VIN2+      | VIN1+     |

ES51992 also configures an input channel rotation (polling) feature. The rotation feature can be activated by setting the ROT bit of STATUS Byte2 to high. In the rotation mode, the actual input channel will be changed by ES51992 sequentially and automatically. The rotation feature has two types, one is for three input channel rotation with the same low input, another one is for two independent differential channel rotation. The following table presents the configuration of the rotation type.

Rotation Type Table:

| ROT | CH1,CH0 | <b>Rotation Type</b>                                         |  |  |

|-----|---------|--------------------------------------------------------------|--|--|

|     | 0,0     |                                                              |  |  |

| TT  | 0,1     | $ch1 \rightarrow ch2 \rightarrow ch3 \rightarrow ch1 \cdots$ |  |  |

| Н   | 1,0     |                                                              |  |  |

|     | 1,1     | $ch1 \rightarrow ch4 \rightarrow ch1 \cdots$                 |  |  |

| L   | -       | Not Rotating                                                 |  |  |

# 4. Special function

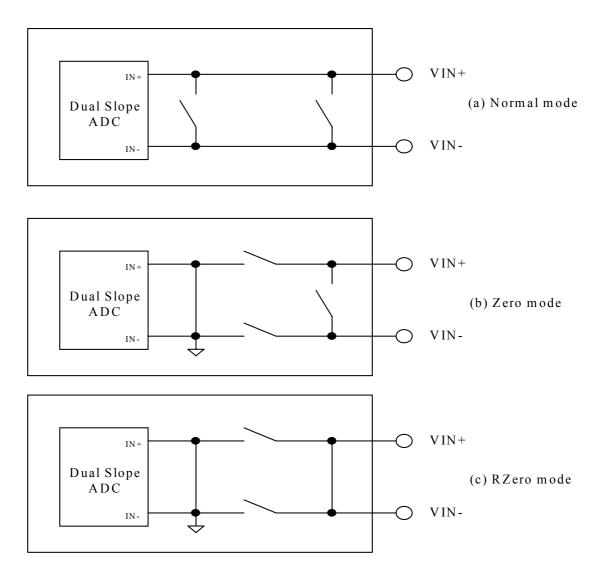

# 4.1 Zero and RZero Calibration

The Zero and RZero calibration are designed for removing the error rise from the propagation delay of internal component. In Zero or RZero calibration mode, ES51992 outputs a calibration value. The normal measurement value must minus the calibration value to cancel the error and obtain a more accurate value. The following block diagram performs the difference between basic structures of normal mode, Zero calibration and RZero Calibration. We suggest users to do zero-calibration in most applications.

# 4.2 Buzzer Setup

When the bit **BUZ** of ID Byte is set to "H", the BUZOUT will output a square signal of MPU I/O swing level to drive a external buzzer. The buzzer frequency is determined by the bits B0/B1/B2 of STATUS Byte3. The configuration of buzzer frequency is listed at the following table.

| B2/B1/B0 | BUZout (kHz) |

|----------|--------------|

| 111      | 4.00         |

| 110      | 3.33         |

| 101      | 3.08         |

| 100      | 2.67         |

| 011      | 2.22         |

| 010      | 2.00         |

| 001      | 1.33         |

| 000      | 1.00         |

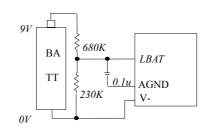

# 4.3 Low Battery Detection

In a case of 3V battery power, the pin LBAT must be shorted to AGND. And the system will have low battery detection level about 2.3V. In another case of 9V or other battery power, the low battery detection happens when the voltage of LBAT is less than -1.23V below GND. And the bit LBAT of STATUS Byte3 will be set to high. A recommended application is shown as following:

The low battery detection level is around 7V

# 4.4 Sleep Mode

When the pin CS is connected to V- or GND (depended on I/O\_control level), the ES51992 will enter sleep mode. In Sleep mode, the chip draws a little supply current. It could extend the battery life. To leave sleep mode or stay in normal mode, the pin CS must be connected to AGND or floating.

# **5. MPU I/O function definition**

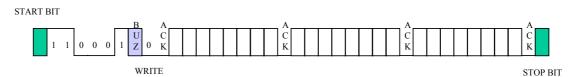

## Write command:

ID byte, Status byte1, Status byte2, Status byte3

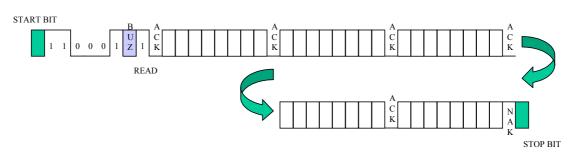

#### Read command:

ID byte, Status byte1, Status byte2, Status byte3, Data byte1, Data byte2

# Start and Stop bit

| ID byte:   |       |           |           |           |      |       |           |

|------------|-------|-----------|-----------|-----------|------|-------|-----------|

| 1          | 1     | 0         | 0         | 0         | 1    | BUZ   | R/W       |

| Status by  | te1:  |           |           |           |      |       |           |

| CH0        | CH1   | <b>C0</b> | C1        | C2        | SIGN | SEL4M | Χ         |

| Status by  | te2:  |           |           |           |      |       |           |

| <b>S60</b> | RZERO | ZERO      | ROT       | Χ         | X    | X     | Χ         |

| Status by  | te3:  |           |           |           |      |       |           |

| 0          | 0     | <b>B0</b> | <b>B1</b> | <b>B2</b> | LBAT | X     | Χ         |

| Data byte  | e1:   |           |           |           |      |       |           |

| D0         | D1    | D2        | D3        | D4        | D5   | D6    | <b>D7</b> |

| Data byte  | 2:    |           |           |           |      |       |           |

| D8         | D9    | D10       | D11       | D12       | D13  | X     | Χ         |

CH1/CH0: ADC input channel selection, the default is [00].

| Code | VIN(+)       | VIN(-)       |

|------|--------------|--------------|

| 00   | VIN0 channel | VIN- channel |

| 01   | VIN1 channel | VIN- channel |

| 10   | VIN2 channel | VIN- channel |

| 11   | VIN2 channel | VIN1 channel |

## C2/C1/C0/S60: Conversion rate selection, the default is [0000]

| C2/C1/C0 | Se                  | 50           |

|----------|---------------------|--------------|

| C2/C1/C0 | L                   | Н            |

| 101      | 128/s               | 128/s        |

| 100      | 96/s                | 96/s         |

| 011      | 64/s                | 76.8/s       |

| 010      | 32/s                | 38.4/s       |

| 001      | 16/s!               | 19.2/s*      |

| 000      | 8/s!                | 9.6/s*       |

| 110      | 3.2/s <sup>!*</sup> | 3.84/s*      |

| 111      | $1.6/s^{!*}$        | $1.92/s^{*}$ |

Crystal: 12MHz

1: 50Hz line noise rejection, \*: 60Hz line noise rejection

SEL4M: "H" is XTAL is 4MHz version, "L" is default 12MHz XTAL

| C2/C1/C0 | S60                 |

|----------|---------------------|

|          | X                   |

| 101      | 128/s               |

| 100      | 64/s                |

| 011      | 64/s                |

| 010      | 32/s                |

| 001      | 16/s!               |

| 000      | 8/s!                |

| 110      | 3.2/s <sup>!*</sup> |

| 111      | $1.6/s^{!*}$        |

Crystal :4MHz

SIGN: "H" is negative, "L" is positive

LBAT: "H" is low battery detection flag active, the default is "L"

RZERO: "H" is RZero calibration mode "ON", the default is "L"

ZERO: "H" is Zero calibration mode "ON", the default is "L"

ROT: Set to "H" to enable multi channel rotating feature

B2/B1/B0: Buzzer frequency selection (independent with conversion rate)

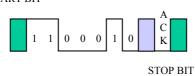

BUZ: "H" is buzzer turn on and "L" is turn off, the default is turn off.

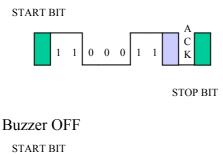

Buzzer ON

**D13-D0**: ADC output data according channel multiplex [CH1/CH0]. Binary code format.

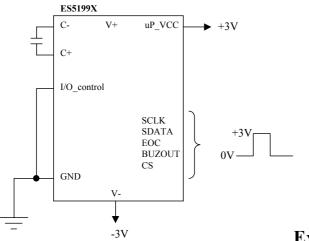

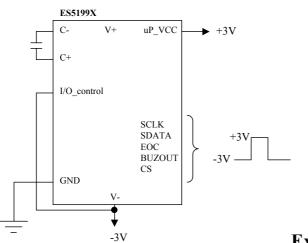

# 6. Power and I/O output level selection

### Power

- Charge pump output for positive supply voltage(V+)

- External DC source to V+ is available by floating the charge pump capacitor

### I/O output level selectable

- uP\_VCC provided by external DC source (the same high level with MPU)

- A control pin (I/O\_control) selects the low level to -3V(V-) or 0V(DGND)

| UP VCC | I/O_control | I/O 1 | Evennele |         |

|--------|-------------|-------|----------|---------|

| uP_VCC |             | Н     | L        | Example |

| 3      | Н           | +3V   | 0V       | Ex.1    |

| 3      | L           | +3V   | -3V      | Ex.2    |

| 0      | L           | 0V    | -3V      | Ex.3    |

# Absolute Maximum Ratings

| Characteristic                  | Rating                       |

|---------------------------------|------------------------------|

| Supply Voltage (V- to AGND)     | -3.6V                        |

| Analog Input Voltage            | V0.6 to V+ +0.6              |

| V+                              | $V+ \ge (AGND/DGND+0.5V)$    |

| AGND/DGND                       | $AGND/DGND \ge (V - 0.5V)$   |

| Digital Input                   | V0.6 to DGND +0.6 or V+ +0.6 |

| Power Dissipation. Flat Package | 500mW                        |

| Operating Temperature           | 0°C to 70°C                  |

| Storage Temperature             | -25°C to 125°C               |

# **DC Electrical Characteristics**

TA=25°C,  $V_{CM}$ =0V, V- = -3V

| Parameter                                                              | Symbol                    | Test Condition                                                                                               | Min.  | Тур.  | Max   | Units             |

|------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

| Power supply                                                           | V-                        |                                                                                                              | -3.3  | -3.0  | -2.5  | V                 |

| Operating supply current<br>Conversion rate = 8/sec                    | $I_{DD}$                  | Normal operation<br>(XTAL=12MHz)                                                                             | _     | 2.0   | 2.2   | mA                |

|                                                                        | I <sub>ss</sub>           | In sleep mode                                                                                                |       | 2.5   | 5     | μA                |

| Voltage roll-over error                                                | REV                       |                                                                                                              | _     |       | ±0.05 | %F.S <sup>1</sup> |

| Voltage nonlinearity                                                   | NLV                       | Best case straight line                                                                                      | _     | _     | ±0.05 | %F.S              |

| Input Leakage                                                          |                           |                                                                                                              |       | 1     | 10    | pA                |

| Low battery flag voltage                                               |                           | V- to AGND                                                                                                   | -2.4  | -2.3  | -2.2  | V                 |

| Internal null high to up. Veg ourrent                                  |                           | $CS (uP_Vcc=3V)$                                                                                             |       | 5     |       | uA                |

| Internal pull-high to uP_Vcc current                                   |                           | CS(uP_Vcc=0V)                                                                                                |       | 1.5   |       |                   |

| Internal pull-low to V- current                                        |                           | I/O_control<br>(V-=-3V)                                                                                      |       | 1.5   |       | uA                |

| Zero input reading                                                     |                           | 10M $\Omega$ input resistor zero cal. by MPU                                                                 | -000  | 000   | +000  | counts            |

| Reference voltage and open circuit voltage for $110\Omega$ measurement | $\mathbf{V}_{\text{REF}}$ | 100KΩ resistor<br>between VRH and<br>AGND                                                                    | -1.33 | -1.23 | -1.13 | V                 |

| Reference voltage temperature coefficient                              | TC <sub>RF</sub>          | 100KΩ resister<br>Between VRH<br>0°C <ta<70°c< td=""><td></td><td>50</td><td></td><td>ppm/°C</td></ta<70°c<> |       | 50    |       | ppm/°C            |

Note:

1.Full Scale

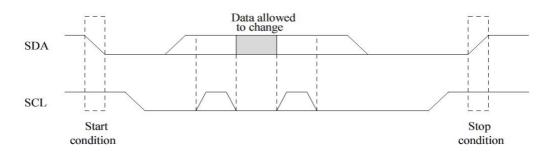

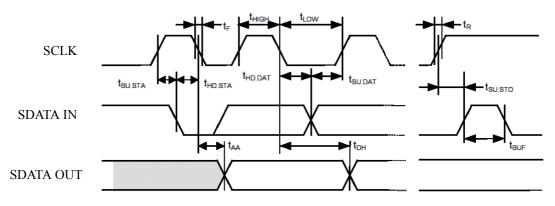

| Parameter                   | Symbol              | Min. | Тур. | Max. | Unit            |  |

|-----------------------------|---------------------|------|------|------|-----------------|--|

| SCLK clock frequency        | f <sub>sclk</sub>   | -    | -    | 100  | kHz             |  |

| SCLK clock time "L"         | t <sub>LOW</sub>    | 4.7  | -    | -    |                 |  |

| SLCK clock time "H"         | t <sub>HIGH</sub>   | 4.0  | -    | -    | us              |  |

| SDATA output delay time     | t <sub>AA</sub>     | 0.1  | -    | 3.5  | .5              |  |

| SDATA output hold time      | t <sub>DH</sub>     | 100  | -    | -    | ns              |  |

| Start condition setup time  | t <sub>su.sta</sub> | 4.7  | -    | -    | - us            |  |

| Start condition hold time   | t <sub>HD.STA</sub> | 4.0  | -    | -    |                 |  |

| Data input setup time       | t <sub>su.dat</sub> | 200  | -    | - ns |                 |  |

| Data input hold time        | t <sub>HD.DAT</sub> | 0    | -    |      |                 |  |

| Stop condition setup time   | t <sub>su.sto</sub> | 4.7  | -    | -    |                 |  |

| SCLK/SDATA rising time      | t <sub>R</sub>      | -    | -    | 1.0  | 1.0<br>0.3<br>- |  |

| SCLK/SDATA falling time     | t <sub>F</sub>      | -    | -    | 0.3  |                 |  |

| Bus release time            | t <sub>BUF</sub>    | 4.7  | -    | -    |                 |  |

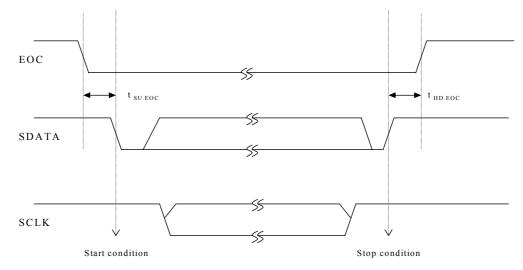

| EOC setup time in read mode | t <sub>SU.EOC</sub> | 0    |      |      | ns              |  |

| EOC hold time in read mode  | t <sub>HD.EOC</sub> | 0    | -    | -    | ns              |  |

# **AC Electrical Characteristics**

# I/O timing diagram

## Read mode EOC timing diagram

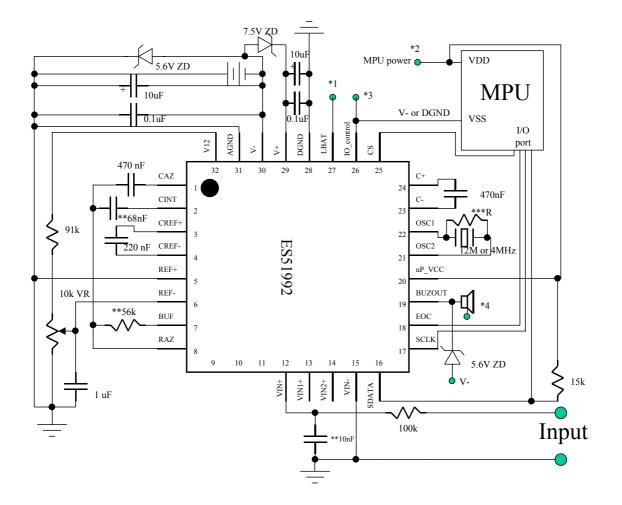

# **Application example**

#### Note:

Zener diodes in above circuit are used for IC protection, so MUST be soldered on PCB first.

#### \*1\*2\*3\*4: Depend on power design

| Depends on conversion rates setting. v 5.0 v |                  |                       |                    |                  |                       |  |  |

|----------------------------------------------|------------------|-----------------------|--------------------|------------------|-----------------------|--|--|

| (a)Conversion rate                           | $(b)C_{INT}(uF)$ | $(c)R_{BUF}(k\Omega)$ | (a)Conversion rate | $(b)C_{INT}(uF)$ | $(c)R_{BUF}(k\Omega)$ |  |  |

| 128/s                                        | 0.01             | 22                    | 16/s               | 0.068            | 27                    |  |  |

| 96/s                                         | 0.01             | 30                    | 9.6/s              | 0.047            | 68                    |  |  |

| 76.8/s                                       | 0.01             | 39                    | 8/s                | 0.068            | 56                    |  |  |

| 64/s                                         | 0.022            | 22                    | 3.84/s             | 0.1              | 82                    |  |  |

| 38.4/s                                       | 0.022            | 36                    | 3.2/s              | 0.1              | 91                    |  |  |

| 32/s                                         | 0.033            | 27                    | 1.92/s             | 0.22             | 68                    |  |  |

| 19.2/s                                       | 0.033            | 47                    | 1.6/s              | 0.22             | 91                    |  |  |

#### \*\* Depends on conversion rates setting: V-=-3.0V

#### \*\*\* R=10~22M $\Omega$ resistor is optional

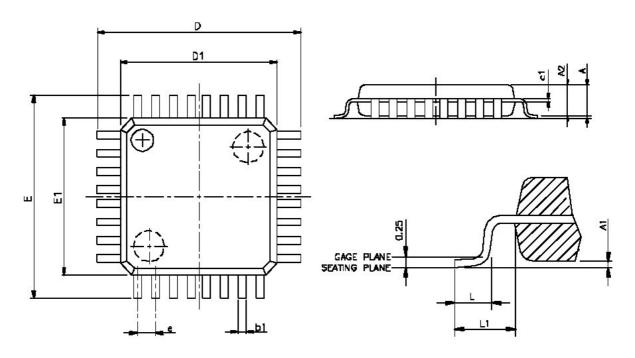

## **Product Outline: LQFP-32**

#### VARIATIONS (ALL DIMENSIONS SHOWN IN MM)

| SYMBOLS    | MIN.     | MAX. |  |

|------------|----------|------|--|

| A          |          | 1.6  |  |

| <b>A</b> 1 | 0.05     | 0.15 |  |

| A2         | 1.35     | 1.45 |  |

| <b>c</b> 1 | 0.09     | 0.16 |  |

| D          | 9.00 BSC |      |  |

| D1         | 7.00 BSC |      |  |

| E          | 9.00 BSC |      |  |

| E1         | 7.00 BSC |      |  |

| e          | 0.8 BSC  |      |  |

| b          | 0.30     | 0.45 |  |

| L          | 0.45     | 0.75 |  |

| L1         | 1 REF    |      |  |

NOTES:

1.JEDEC OUTLINE:MS-026 BBA

- 2.DIMENSIONS D1 AND E1 D0 NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25mm PER SIDE. D1 AND E1 ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS IMCLUDING MOLD MISMATCH.

- 3.DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION.ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM & DIMENSION BY MORE THAN 0.08mm.